快訊

- 【一文看懂】如果南韓政府強行介入三星罷工 會怎麼做?

- 快訊/李在明批評三星電子工會「要求過分」:分享利潤的主體應是資方而非工會

- 快訊/4月外銷訂單874.5億美元 歷年單月次高 連15紅

- 蔣萬安棄綠卡填「Taiwan」引討論 殷瑋反問:寫台灣怎麼了嗎?

- 日本岩手一老翁陳屍溪谷中 疑是岩手今年第二個熊殺人案例

- 旅遊勝地淪漢他病毒疫情源頭?阿根廷設陷阱捕鼠找真相

- 三重滅門案一審判死刑!軟飯男厭世臉出庭「延押沒意見」 冷眼回應改判問題

- 穿「Taiwan」T恤健走遭世衛阻擋 外交部不忍了:已向WHO與警方抗議

- 總統拋千億助中小微企業轉型 經長透露正研擬將「升級轉型條例法制化」

- 中國多省暴雨釀洪災 至少12死20失蹤、數萬人撤離

- 北院還在等!柯文哲案上不了二審 卡關一審全因「她」

- 辜仲諒想飛菲律賓拚棒球!運動部這人打包票「不會跑」 高院准3億交保換出境

- 近30國議員聲援 IPAC:任何攸關台灣前途討論都必須有台灣參與

- 搞定黨代表抽菸爭議 國民黨今年全代會續於成功高中舉辦盼年底選戰成功

- 輝達亞太研發中心+1!聯手新加坡重押「這領域」 OpenAI也來了

- 泰國擬取消對93國60天免簽 外交部:尊重泰方決定

- 眼科診所「電梯斷頭」清潔阿姨死因出爐 「不可能會這樣!」尪崩潰

- 談判破裂!三星工會宣布明起全面罷工 台股記憶體股聞訊走強

- 替兒子曾煥嘉撇貪污!新北老議員認了聘「假員工真助理」 被質疑違法回這句

- 吸胸頭埋雙腿!色狼庭長二審重判3年10月 高檢署聲請限制出境出海慘遭打臉

【決戰矽光子2-1】藉「光速」挑戰電子物理極限!一文看懂矽光子為何爆紅

2024-06-30 07:35 / 作者 戴嘉芬

護國神山台積電因應客戶需求,也投入矽光子研發。目前研發大本營位於新竹寶山鄉。路透社資料照

在 AI、HPC 等應用推動下,雲端資料中心承擔爆炸性傳輸量,傳統纜線的電子訊號傳輸已不敷使用。與傳統的電子訊號相較,光訊號具備高頻寬、低功耗、傳輸距離更遠等特點。而「矽光子」技術將光學元件用矽製程整合成晶片,把訊號由電轉為光,傳輸介質由銅導線轉為光波導,解決訊號衰減、散熱等問題,成為資料中心下一個解方。矽光子(Silicon Photonics)是透過CMOS(互補式金屬氧化物半導體)的技術,在矽晶片上整合了光電的通訊模組,以光訊號來做傳輸,以電訊號來做運算,是一種使用矽製程半導體技術所製造的光學晶片。

工研院產科國際所分析師張筠苡指出,這種技術涉及多種的光電訊號轉換,同時還需要微縮到積體電路以下的維度,因此具有相當高的技術門檻。

另一位分析師劉美君也指出,由於電子的物理極限,半導體微縮過程中會產生發熱延遲,讓傳輸速度變慢,所以需要利用光訊號來傳輸,光的能量一旦夠強,光波會變成粒子,稱為光子。光子的大小比電子小很多,而且傳輸時以「光速」在傳,能解決發熱問題。如今電子結構已無法解決散熱問題,但光子發熱問題少,相對比較不耗電,這是矽光子另一大優勢。

共同光學封裝(CPO;Co-Packaged Optics)是目前矽光子能做到的技術進展。CPO透過先進封裝技術將光子積體電路(PIC)與電子積體電路(EIC)整合在同一個基板上,來提升互連頻寬與傳輸效率。優點是減少光引擎與ASIC之間的連接距離,同時解決訊號損失的問題,因此,CPO可以說是實現矽光子在光電互連的一個重要階段。

工研院產科國際所分析師張筠苡指出,共同封裝光學CPO市場規模預計在2028年達到4050萬美元。戴嘉芬攝

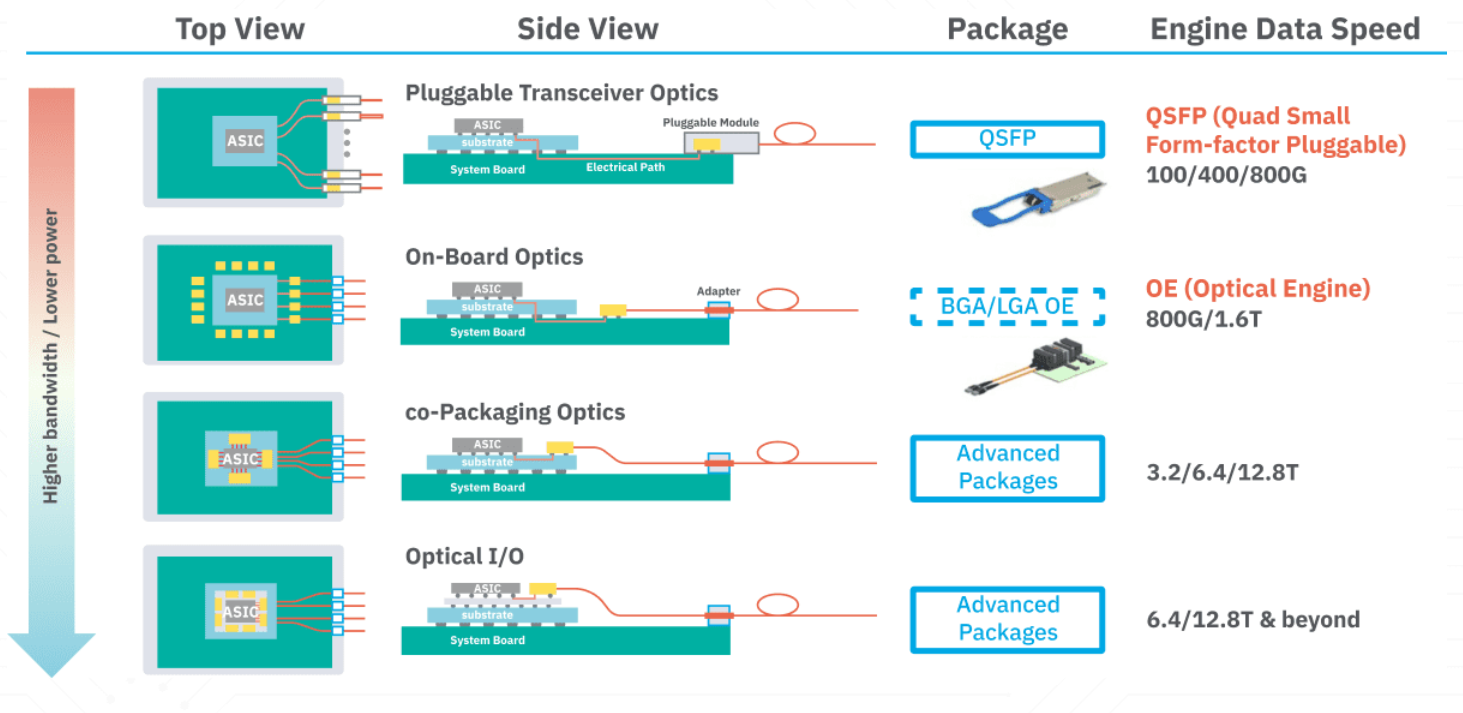

張筠苡指出,從2000年至今,市場仍以可插拔(Pluggable)光學元件為主,並朝OBO(On-Board Optics)、NPO(Near-Package Optics)型態發展,NPO、OBO都是邁向CPO之前的過渡型態。這期間,業者朝縮短光學模組跟ASIC晶片之間的距離作為研發方向,像是NPO就是在中間多放一層高性能PCB(印刷電路板),對ASIC和光學模組進行更高效整合,以提升傳輸速率,並保有訊號完整性。

CPO共同封裝光學技術架構的演變。翻攝日月光官網

國內投入矽光子研發以晶圓代工龍頭台積電和封測龍頭日月光為主。其中,日月光在此領域已耕耘十多年,日月光投控營運長吳田玉表示,矽光子技術必須長期耕耘,台灣在全球半導體產業已大贏,若繼續掌握矽光子技術,台灣半導體產業可謂如虎添翼,絕對不能放掉矽光子技術,日月光會持續研發和投資。

日月光投控營運長吳田玉本週在股東會後表示,台灣半導體產業絕對不能放掉矽光子技術。日月光提供

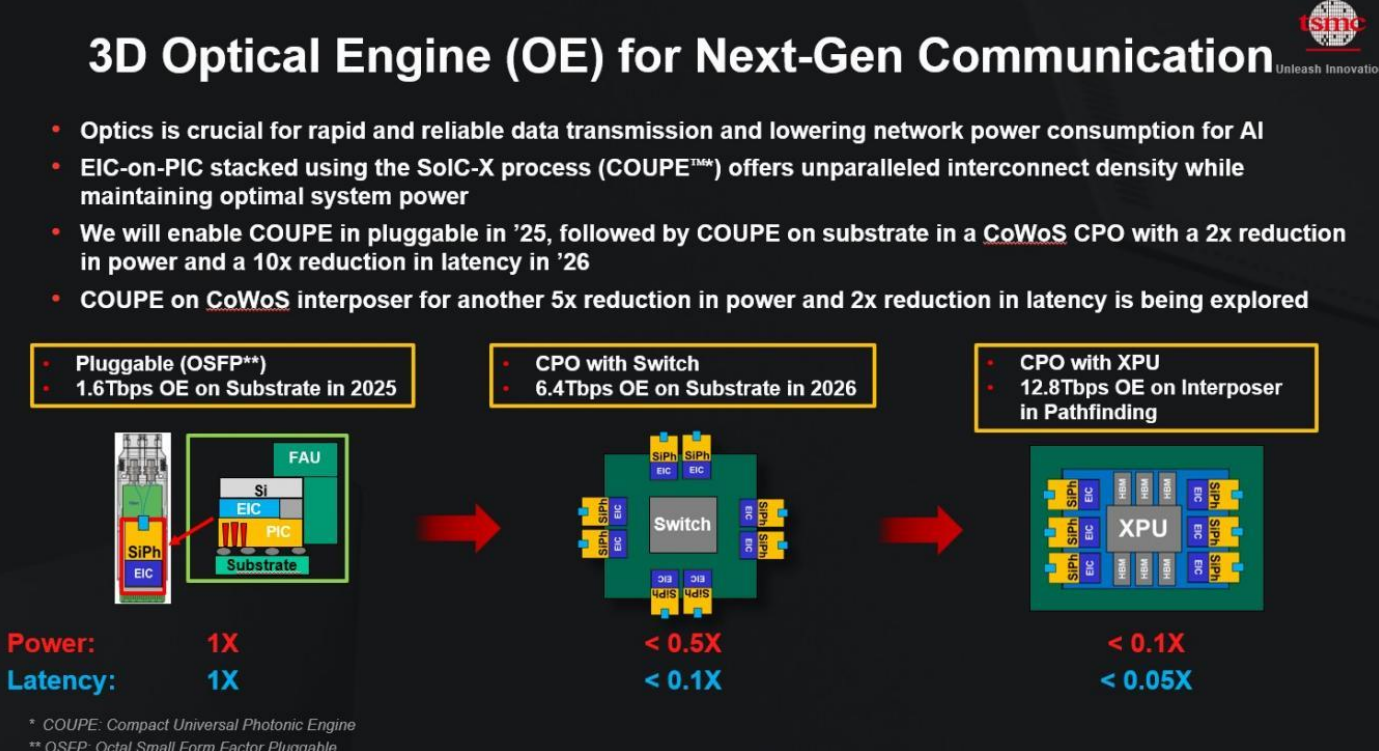

至於台積電在矽光子領域研發以「COUPE;緊湊型通用光子引擎」技術為主,COUPE使用SoIC-X晶片堆疊技術將電子裸晶堆疊在光子裸晶之上,相較於傳統的堆疊方式,能夠為裸晶對裸晶介面提供最低的電阻及更高的能源效率,能支援AI熱潮帶來的數據傳輸爆炸性成長。

在研發進程上,台積電預計於2025年完成支援小型插拔式連接器的COUPE驗證,接著於2026年將其整合於共同封裝光學元件的CoWoS封裝基板,將光連結直接導入封裝中。藉此可降低2X功耗、將延遲降低10X。

台積電還在探索一種更為先進的共同封裝光學元件方案,將COUPE整合於CoWoS中介層,進而將功耗再降低5X、將延遲再降低2X。台積電表示,矽光子是共同封裝光學元件的最佳選擇,因為其與半導體相容,且可與EIC/PIC/交換器在封裝層高度整合。

台積電正在開發用於下一代通訊的3D光學引擎技術,目標是將COUPE整合於CoWoS中介層,進一步降低功耗和延遲。取自TSMC

最新more>

- 陪伴台北人62年!「西門町in89豪華影城」5月底歇業 「最雷第9廳」走入歷史

- 【每日揭詐】聽信假檢警恐嚇陷無底洞!狂買實體黃金證清白 家人急攔截驚覺數十年積蓄成空

- 快訊/4月外銷訂單874.5億美元 歷年單月次高 連15紅

- 「哈登一場要運球1000次」尼克教頭揭密落後22分大逆轉的心理戰

- 蔣萬安大展政績!談大巨蛋變經濟引擎 曝輝達落腳北士科內幕

- 賴清德喊「0到18歲」月發5000 林智群批太天真:不生未必是沒錢

- 賴清德520暢談政績 鄭麗文「2笑」反酸:談話充滿謊言,怎麼說的出口

- 蔣萬安棄綠卡填「Taiwan」引討論 殷瑋反問:寫台灣怎麼了嗎?

- 日本岩手一老翁陳屍溪谷中 疑是岩手今年第二個熊殺人案例

- 蔣萬安問是否刪除台獨黨綱?吳崢嗆:應先問鄭麗文 依照國民黨黨綱有沒有要反共?

熱門more>

- 張凌赫「唯一交往女友」爆新戀情 白鹿和小6歲男神待同小區!官方認1事

- 心臟移植童點餐註明:不要生菜 摩斯漢堡員工「回覆1紙條」暖爆7萬人

- 離譜!一家人狂打9歲童「母冷眼旁觀」 他忍痛深夜衝超商求救

- 擎天崗「情侶打砲」爆紅掀朝聖!「恐龍野戰」深夜湧5000人線上圍觀

- 【獨家】不讓小玉減刑!鄭家純拖到「他確定入獄」才和解 討犯罪所得結果曝

- 嘉義驚爆國中生遭9同學持鋁棍、水泥塊痛毆逼下跪 法官一原因判「非霸凌」

- 阿信助理「扶正祕辛」又被扒 緋聞對象盤點!唯一公開戀情是她

- 台股崩盤說再起? 謝金河:台積電撐著不會崩盤 呼籲政府快對公務員、醫護調薪

- 轟「鳳梨」吳泓逸12槍 他逃亡10個月曬機票返台歸案!檢方證實1事

- 柯案二審備戰!高院先祭「柯文哲條款」防法官落跑 貪污庭12人請調添變數