快訊

- 台灣半數房屋持有者為60歲以上長者 房屋稅女性納稅占比升45.2%再創高

- 川普滿手好牌、面對習近平難占上風?CNN:美國選民恐成關鍵因素

- 《少康戰情室》引用讀者投書被控侵權 趙少康獲不起訴

- 中國央視:盧比歐表示中美關係非常有建設性 世界穩定是所有人之福

- 中信兄弟鄭浩均「被打爆還笑」!辜仲諒妙回:要打屁股,回去再教育

- 川習會高規格登場 WSJ:美國的未來其實更仰賴台灣

- 「川習會」衝擊台灣經濟?經長龔明鑫:台美經貿關係持續深化不受影響

- 恩智浦攜廣達 加速推動軟體定義汽車確定性區域網路發展

- 路透:美早批准10家中國公司買H200晶片 北京不放行、黃仁勳求突破

- 鈺創旗下帝濶合規隱私 AI 影像去識別化系統 協助醫療醫美業建立可信任安全管理

- 林志玲接文策院董事 賈永婕喊「好險」:我還是最美董事長

- 鴻海Q1三率三升資本支出增3成! 輪值CEO蔣集恆:Q2 全年皆強、能見度比3月更佳

- 核二凌晨驚傳失火 經長龔明鑫:疑似電線走火

- 穎崴CPO論壇登場 預告光學引擎將成通訊關鍵技術

- 再興中學實驗室起火燒傷學生! 家長怒告校長、教師7人結果曝光

- 組「國家隊」搶救森崴又德風場? 經長龔明鑫:這是好風場、尊重業者

- 中國又創新名詞 習近平:美中新定位「建設性戰略穩定關係」

- 對川普當頭嘲諷? 中國恢復美牛進口許可馬上又撤銷

- 政院拍板修能管法 能源大戶需設置自發自用儲能設施

- 習近平定調台灣是「中美關係中最重要的問題」 外媒:措辭比9年前更嚴厲

AI晶片競爭新時代! 蔡力行:能效創新外、記憶體和先進封裝成為關鍵驅動力

2026-02-21 11:29 / 作者 陳俐妏

聯發科執行長蔡力行。翻攝自聯發科官網

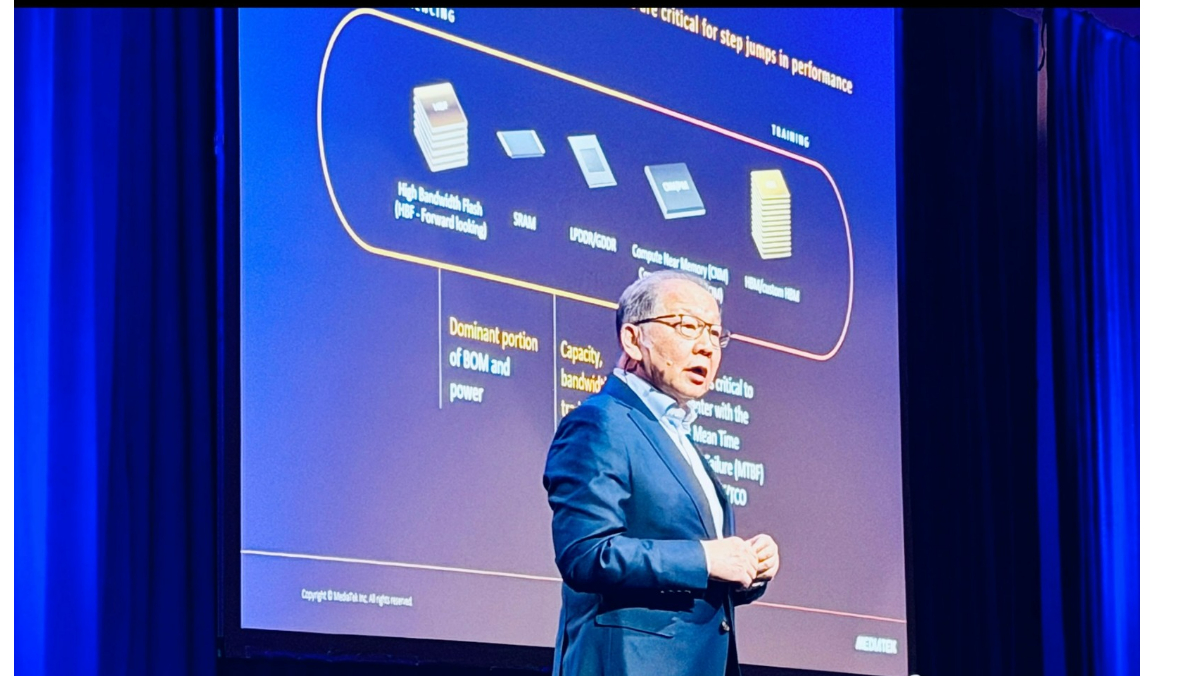

聯發科執行長蔡力行 在2026 ISSCC 國際固態電路會議發表專題演講,聚焦半導體產業如何因應AI 運算需求。蔡力行表示,未來 AI 競逐的勝負,不再只是比誰的晶片快,將會以最低能耗與總體成本,打造可規模化落地的運算系統,但能源依然是至今推動創新最大的限制在能效創新上,將會有三大趨勢,包括:設計技術協同優化(DTCO)、供電技術,以及運算架構的進步,而關鍵驅動力將是記憶體與先進封裝技術的突破。

ISSCC是半導體IC設計領域的最高殿堂,蔡力行本次將進行大會演講,探討先進封裝、電力供應、散熱管理、高頻寬記憶體、高速介面及無線通訊等半導體關鍵技術,如何影響未來十年AI系統的發展。此外,也將說明半導體產業生態系和供應鏈如何透過效能、效率、擴展性架構,以及跨層次系統的創新合作,推動運算能力、頻寬和能源效率的快速成長,進而加速agentic AI和physical AI的普及。

聯發科本次入選有IC設計界奧林匹克之稱的ISSCC 2026論文中,有兩篇由台灣總部研發團隊發表,這也讓聯發科成為台灣業界唯一連續23年累計超過百篇論文入選的企業。

AI 運算需求帶動爆發性成長,但蔡力行指出,能源依然是至今推動創新最大的限制,但同時也是推動創新的催化劑。半導體在能效創新上,將會有三大趨勢,包括:設計技術協同優化(DTCO)、供電技術,以及運算架構的進步,正持續推動效率提升。

而聚焦半導體關鍵驅動力,蔡力行認為,記憶體與先進封裝技術的突破,將成為引領下一波進展的關鍵動能。

蔡力行也提出下一個十年半導體技術指標的目標與願景,包括:光罩尺寸突破 40 倍、頻寬密度提升 20 倍

、電源與散熱密度提升 20 倍、運算效能每瓦效提升 100 倍來邁進。

最新more>

- 開地圖砲挨告3連敗!吳子嘉諷名嘴「雜碎」嗆口交 一審判賠20萬

- 台灣半數房屋持有者為60歲以上長者 房屋稅女性納稅占比升45.2%再創高

- 川普滿手好牌、面對習近平難占上風?CNN:美國選民恐成關鍵因素

- 《少康戰情室》引用讀者投書被控侵權 趙少康獲不起訴

- 醫美偷拍風暴滾雪球!台中樂菲診所驚見「可疑孔洞」 錄影主機被扣押

- 中國央視:盧比歐表示中美關係非常有建設性 世界穩定是所有人之福

- 不反美了?央視突插播《功夫熊貓》掀熱議 網瘋傳:本要安排《孫子從美國來》

- 半數民眾不知「如何與思覺失調症患者互動」 醫生教你這樣做!

- 民代爆高市府標案也有「聶永真模式」?陳其邁:皆依法招標

- 馬克宏遭妻「推臉」有內幕?傳訊息誇女星「漂亮」 碧姬當場氣炸

熱門more>

- 悚!清大台積館女學生墜樓亡

- 張凌赫情史「只和她交往過」 白鹿1句話遭網暴!三天掉10萬粉

- 台中狠媽「11樓丟下剛出生兒子」報復男友 不認殺人!求緩刑

- 坐牢前押身家抄底一股票!出獄後一看「暴賺40000%」 資產飆破23億

- 快遞禮物竟變惡魔!FedEx司機綁架勒殺7歲女童 「她哭喊錄音曝光」家人心碎

- 蘇飛雅談星》2026下半年運勢一次看!火象翻身、風象續紅 「最強星座」曝光

- 北市高資產點閱榜首選?揭曉年度五大熱門豪宅 中正區「這棟」奪冠

- 中國若併吞台灣將如何治理?智庫:大舉清洗、再教育、長期監控審查

- 又有人升官!台積電宣布擢升李俊賢等4名高層

- 國票金改選「變天」在即! 路透爆料:下一步規劃與公股金控整併 「這家」呼聲高