快訊

- 川賴將通話?外交部回應了

- 民眾黨退黨再+1!楊寶楨宣布獨立參選 指「不認同黨內霸凌文化」

- 快訊/川普表示將與賴清德通話 可能直接討論對台軍售

- 經趙少康與黨中央多次駁火後 傅崐萁晚間邀趙、郝餐敘引發聯想

- 快訊/南韓三星電子宣布暫緩罷工 薪酬方案週六交付投票

- 疑不明無人機入侵 立陶宛發布國家級警報、防長與國會議員躲地下室避難

- 潛艦後續艦預算100%恐全凍 台船:韌性防衛已就位籲請在野黨團勿斷炊

- 認罪了!李四川胞弟李賜福「恐嚇取財」願調解 法官裁定簡式審判

- 就職2週年 鄭麗君嘆:立法院阻礙無人機產業發展

- 火箭砲劃過富士山腳下!美軍第二度試射海馬士

- 擠下郭台銘!國巨陳泰銘身家破4900億 首次登頂台灣首富

- 馬英九基金會再發「捉字眼」聲明 質疑李德維等3人小組杯葛董事會召開

- 普丁發言人表示 不排除趁APEC峰會舉行與川普的「普普會」

- 藍委質疑戰備彈藥儲量 顧立雄:加14條產線、儲量增至120天預算被刪了

- 今年第一季Meta平台詐騙逾13億6千萬 打詐中心點名要求修正技術漏洞

- 研究:氣喘病常用藥 可望用來對抗癌症

- 「工作做不完」中市海線輔具中心女員工輕生 盧秀燕不知情…議員痛批KPI訂錯

- 捷運萬大線LG11站「捨直取彎」進公園! 民團打官司敗訴定讞

- 德國再抓共諜 中國人夫婦涉嫌刺探軍事科技

- 北檢深入萬華分局 建立橫向連繫嚴查選舉不法行為

乾瞻完成符合UCIE 2.0標準之 TSMC SoIC製程設計定案

2025-07-15 17:03 / 作者 陳俐妏

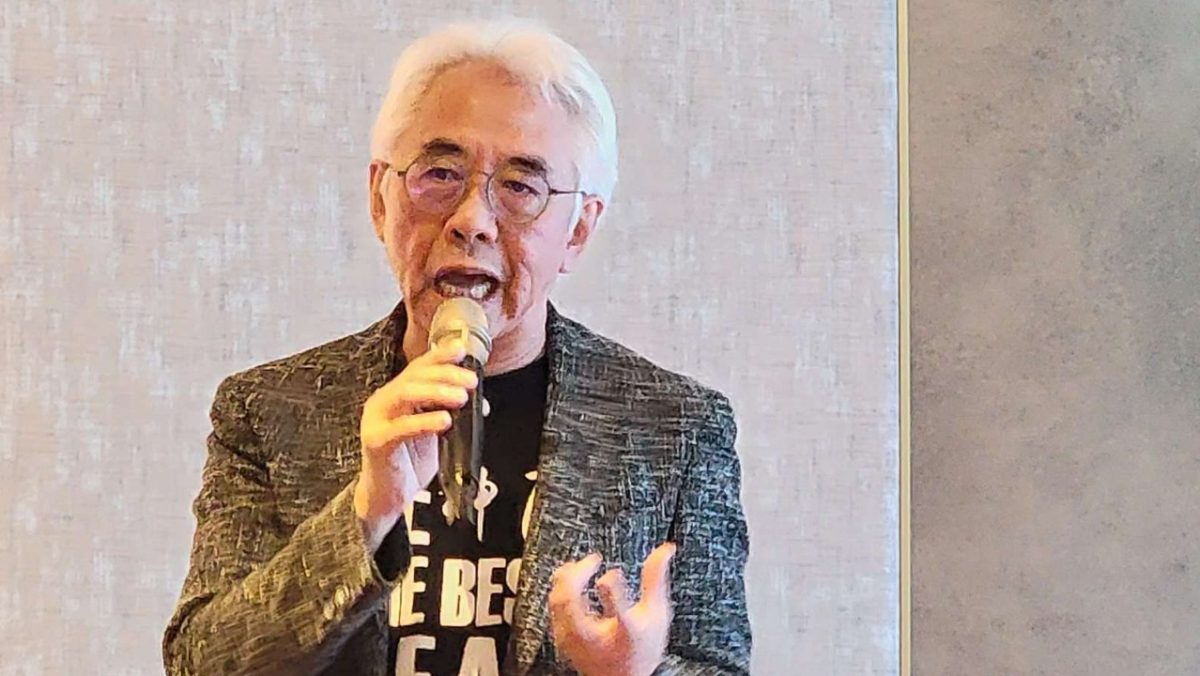

神盾董事長羅森洲。陳俐妏攝

神盾集團旗下矽智財(IP)解決方案廠乾瞻科技(InPsytech),近日正式宣佈完成符合UCIE 2.0(Universal Chiplet Interconnect Express)標準的台積電Face-to-Face SoIC先進製程設計定案,成功實現異質整合晶片的高速互連能力。乾瞻也將同步推出對應 TSMC SoIC先進製程的完整晶圓級與封裝級設計驗證解決方案,加速 IC 設計公司晶片開發與驗證的流程。神盾表示,這次設計採用TSV(Through-Silicon Via)技術以實現訊號傳輸與電源供應,不僅大幅提升3D堆疊異質整合晶片的設計彈性,也強化整合效能。為協助客戶加速從設計至量產的導入過程,乾瞻同步推出對應 TSMC SoIC先進製程的完整晶圓級與封裝級設計驗證解決方案,加速 IC 設計公司晶片開發與驗證的流程。

繼日前加入英特爾晶圓代工加速 IP 聯盟與三星 SAFIP 計畫後,乾瞻已為英特爾與三星的 IP 夥伴,並陸續將自家先進產品導入兩大晶圓廠生態系統,以協助客戶強化其先進半導體產品競爭力。此3D異質整合與高速互連的設計,特別適用於高效能運算(HPC)伺服器與邊緣AI裝置,可有效提升AI推論與資料處理效率,滿足低延遲與高頻寬需求。

乾瞻科技總經理羅時豪表示,此次順利完成設計定案,除自身團隊的投入外,更要感謝半導體產業合作夥伴,這也代表著客戶對乾瞻技術實力的高度肯定。乾瞻科技將持續以技術創新為驅動核心,不僅深化與海內外團隊的協作,也致力於服務全球客戶,共同打造更先進、卓越的科技環境。

最新more>

熱門more>

- 北科大傳研究生墜樓亡 友人悲曝生前長期遭指導教授霸凌

- 心臟移植童點餐註明:不要生菜 摩斯漢堡員工「回覆1紙條」暖爆7萬人

- 張凌赫「唯一交往女友」爆新戀情 白鹿和小6歲男神待同小區!官方認1事

- 【獨家】不讓小玉減刑!鄭家純拖到「他確定入獄」才和解 討犯罪所得結果曝

- 離譜!一家人狂打9歲童「母冷眼旁觀」 他忍痛深夜衝超商求救

- 從背後偷抱女友被認定「性騷」!政大生告輸學校 法院斥:伴侶不是洩慾工具

- 台股崩盤說再起? 謝金河:台積電撐著不會崩盤 呼籲政府快對公務員、醫護調薪

- 嘉義驚爆國中生遭9同學持鋁棍、水泥塊痛毆逼下跪 法官一原因判「非霸凌」

- 快訊/政府時限已過 三星電子大罷工談判仍無結果、調解失敗將進入罷工

- 【快訊】三星勞資談判破局!工會宣布:明日開始大罷工