快訊

- 批徐國勇「台灣沒光復節」搞意識形態 蔣萬安:賴清德是哪國總統?

- 快訊/供電吃緊!台電再掉1部機 林口1也故障 今晚備轉率「保6」難!

- 苗博雅控「聲援」納粹青年 羅智強提告求償500萬元

- 17歲黑道小弟涉案!姊弟戀4步驟預謀殺人 爽躺星級賓館遭捕畫面曝

- 黑幫少年「44秒33刀」砍死女大生 驚爆:不是女方劈腿!只想討回錢繳學費

- 「挑秘書像在選妃」前原能會主委涉職場霸凌、性別歧視 懲戒法院罰俸60萬

- 川普訪英帶大禮!輝達、微軟各宣布投資英國數千億

- 「萊爾校長」紓壓球今首波開賣被秒殺 朱立倫:凸顯賴清德執政問題

- 徐國勇附和「台灣地位未定論」 朱立倫:賴清德是託管地總督、特首?

- 黨主席選舉煙硝四起 朱立倫:每位都大家加油

- 降息激勵科技股一年強漲逾六成 標普科技精選ETF買點到

- 警員涉入詐團!提供驗證碼做假投資詐騙 前保安大隊隊員一審判3年6月

- 美:重振與太平洋島國關係 與台灣攜手擴大區域電纜

- 竹科工程師70秒灌下「1公升的眼淚」喝到掛 酒吧店長、負責人被起訴

- iPhone升級iOS 26「耗電又發燙」 蘋果承認了!官網親自解答

- 范姜彥豐爆婚變粿粿!啦啦隊女神甜喊「一日男友」遭炎上 哽咽道歉了

- 中共黨媒稱與美交易TikTok「共贏」 籲取消限制措施、不搞集體霸凌

- 南韓外長:習近平應該會赴韓參加APEC峰會

- 快做防颱準備!準颱風樺加沙預估「中颱起跳」 下週這時間最靠近台灣

- 相驗結果曝!女大生遭17歲男友奪命「刀傷集中頭頸」:仗著未成年,不會判死刑

【技術論壇懶人包】台積電A14量產時程、先進封裝、下一代電晶體及矽光子進展一文看懂

2025-05-15 17:10 / 作者 戴嘉芬

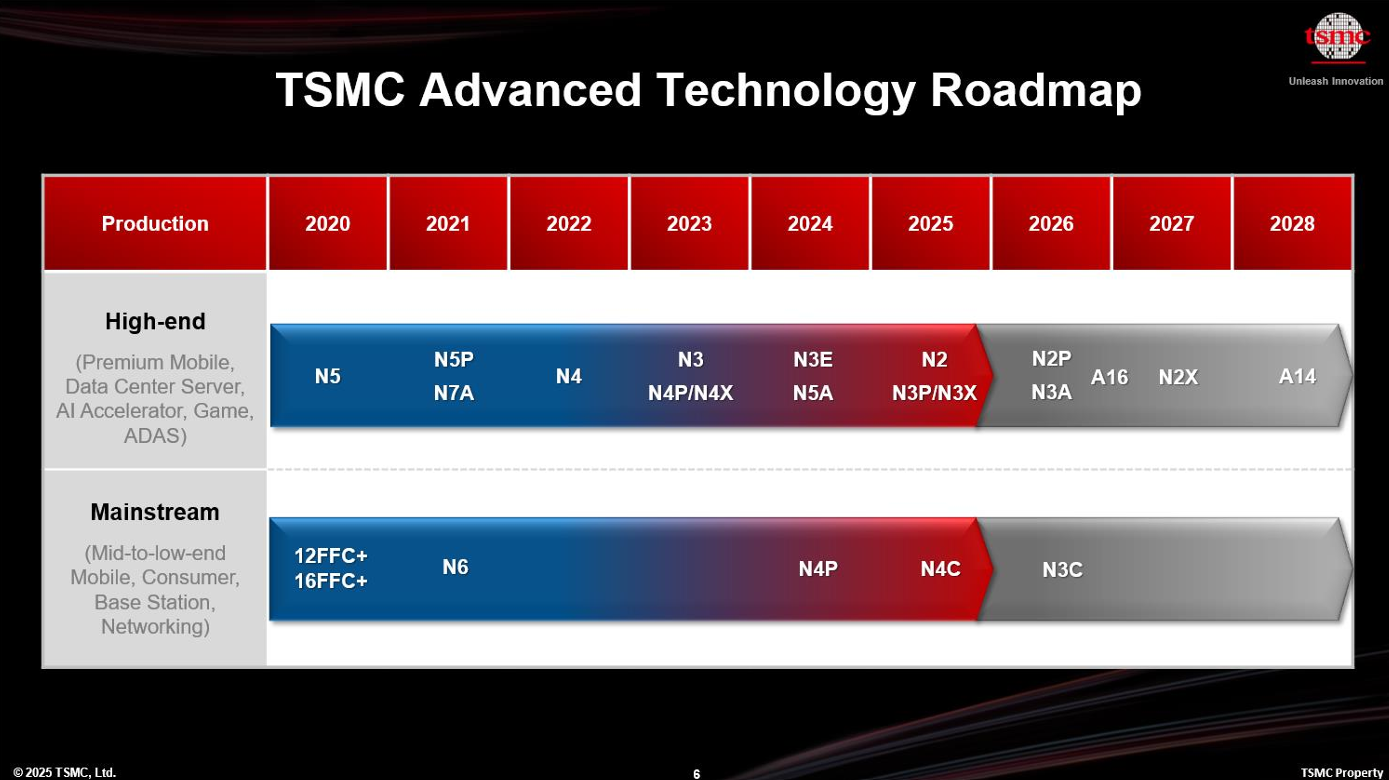

台積電業務開發資深副總暨副共同營運長張曉強在論壇中,提到A14與2奈米的差異。取自TSMC

全球晶圓代工龍頭台積電今日(5/15)在新竹舉辦技術論壇,會中揭示半導體先進製程如2奈米、A16、A14以及先進封裝如 InFo、CoWoS、SoW 系統級晶圓技術進展。論壇中還提到下一代電晶體微縮技術 CFET,同時也透過2D材料的電晶體,發展出最薄的電晶體通道。此外,也探討特殊製程、車用級先進封裝以及矽光子等技術的進展。

台積電15日於新竹舉辦2025年技術論壇,揭示A14先進製程技術優勢。取自TSMC

台積電業務開發資深副總暨副共同營運長張曉強在論壇中指出,預計到了2030年,半導體市場將達到 1兆美元,由高效能運算(HPC)(45%)、智慧型手機(25%)、汽車(15%)和物聯網(10%)等應用主導。為了因應龐大市場需求,台積電持續精進先進製程,以符合客戶成長;台積電先進製程技術包括甫於北美技術論壇發表的A14,以及A16和2奈米。

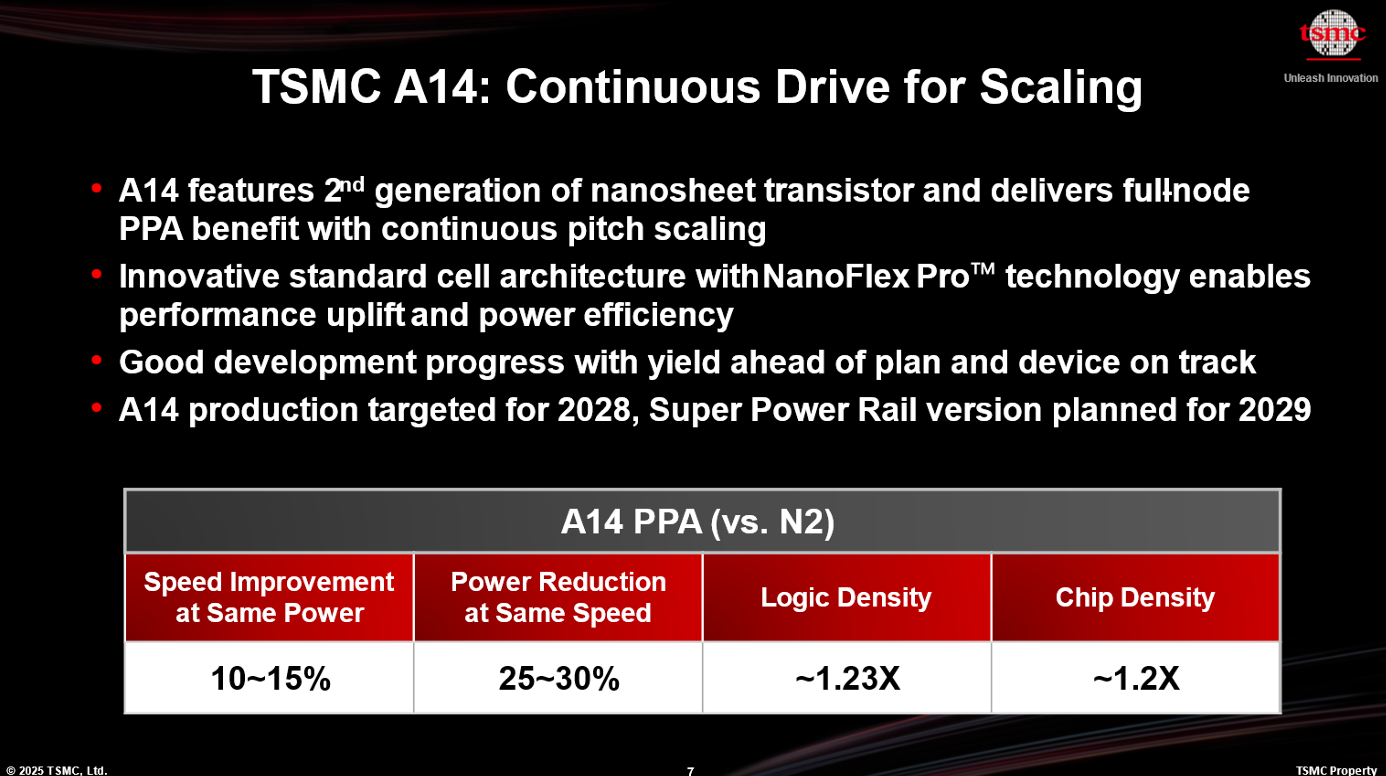

依台積電製程藍圖,A14將於2028年量產,A14的超級電軌版本預計2029年量產。取自TSMC

張曉強說,A14將以更強大的運算能力和更高的能源效率加速AI發展的里程碑,並增強智慧型手機的內建AI功能。與2奈米製程技術相比,在相同功耗下,A14速度提升達15%;而在相同速度下,功率降低達 30%,邏輯密度增加超過20%。

與2奈米相比,台積電A14技術在相同功耗下,速度提升15%。取自TSMC

他繼續指出,A14將採用新的NanoFlex Pro技術,以實現更高的效能、能源效率和設計靈活性。A14計劃於2028年開始生產,搭載超級電軌技術(Super Power Rail, SPR)的版本則計劃於2029年推出。

提到A16製程,張曉強指出,A16製程對於訊號路由和供電要求嚴苛的資料中心AI/HPC產品,為其提供業界最佳的背面供電技術和優化的邏輯密度。A16計劃於2026年下半年量產。

台積電2奈米依計畫在今年下半年量產,256Mb的SRAM平均良率超過90%。2奈米第二年的新設計定案(tape-outs)數量比同期的5奈米增長4 倍。2奈米家族包括N2P、N2X,N2P依計畫在2026年下半年量產,與N3E製程技術相比,N2P在相同功耗下,速度提升18%;而在相同速度下,功率降低約36%,邏輯密度增加1.2倍。N2X 將提供約10%最大時脈頻率,並計劃於2027年量產。

張曉強說,3奈米是一個高產量且長期生產的技術,截至2025年4月,已有超過70個新的設計定案。3奈米家族包括N3E、N3P、N3X和N3C。

其中,N3E正為旗艦的行動和HPC / AI產品進行高度量產。N3P將於2024年第四季進入量產。N3A係針對汽車應用,包括駕駛輔助和自動駕駛技術,目前正在進行最終缺陷改善,有望獲得AEC-Q100一級認證,將於2025年稍晚生產就緒。至於N3X致力為客戶CPU產品突破效能極限;N3C則為價值優先的產品提升成本效益。

台積電3奈米家族包括N3E、N3P、N3X、N3A以及N3C。取自TSMC

張曉強提到,互補式場效電晶體(CFET)設計是很有前景的微縮技術候選,可滿足越來越多在緊湊外形尺寸中提高效能和降低功耗的需求;透過將 nFET 和 pFET 垂直堆疊,CFET實現近兩倍的電晶體密度。台積電將nFET和pFET整合於同一晶圓中,並展示了具備48奈米閘極間距、世界上最小的CFET逆變器。

此外,台積電在採用2D材料的電晶體方面取得進展,發展出研究組合中,最薄的電晶體通道;同時展示了第一個在類似於2奈米技術的堆疊奈米片電晶體架構中,採用單層通道的電氣性能。

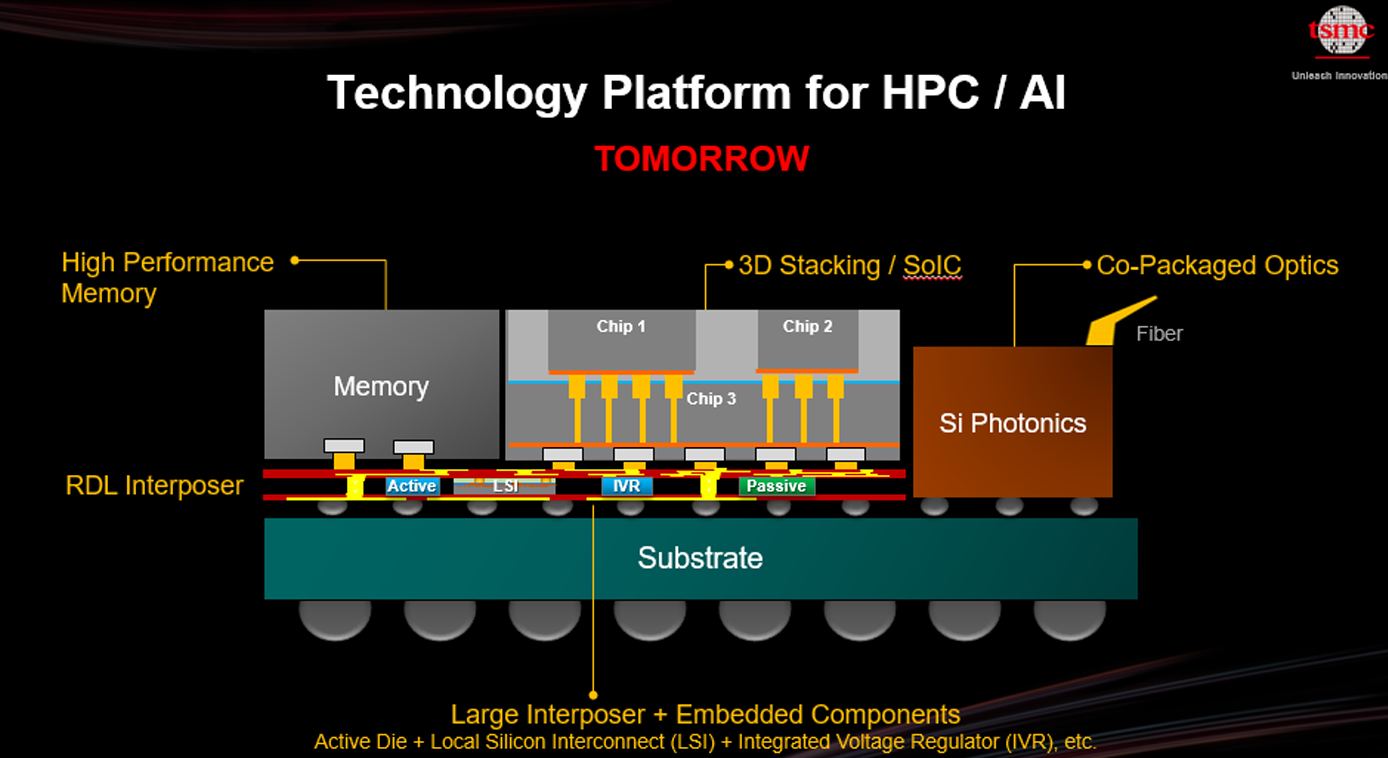

台積電3DFabric先進封裝技術提供SoIC、InFO、CoWoS平台讓客戶選擇。其中,SoIC平台用於3D矽堆疊,由SoIC-P和SoIC-X兩種堆疊方案組成,用於N3-on-N4堆疊的SoIC技術將於2025年進入量產,其間距為6μm;下一世代SoIC A14-on-N2將於2029年就緒。InFO PoP和InFO-3D針對高階行動應用,InFO 2.5D則用於HPC的小晶片整合。

在CoWoS技術進展部分,基於矽中介層的CoWoS-S和基於RDL中介層的CoWoS-L和CoWoS-R,目的在為HPC應用整合先進邏輯和HBM,且讓更大的光罩尺寸使更多的晶圓可以整合到同一個封裝中,這樣可以更有效地將多個較小的晶片(小晶片)和記憶體堆疊(如HBM)整合到一個單獨且較大的中介層上。

其中,5.5倍光罩尺寸的CoWoS-L技術將於2026年推出;而台積電正在透過9.5倍光罩尺寸的CoWoS突破界限,計劃於2027年量產,此一尺寸可在一個封裝中整合12個或更多的HBM堆疊,結合台積電先進邏輯晶片技術,支援更大的AI加速器設計。

張曉強指出,此技術的創新之處在於整合邏輯晶片和HBM(晶圓級整合),可滿足AI訓練對運算能力激增的需求。SoW平台將所有必要的元件整合在一起,例如連接器、電源模組和冷卻模組。其中,台積電SoW-X是一款基於CoWoS技術和晶圓尺寸的系統,運算能力比現有的CoWoS解決方案高40倍,與整座伺服器機架相當,SoW-X計劃於2027年量產。

台積電針對特殊製程提供各種解決方案,其中包括業界首款HBM基礎裸晶(Base Die),採用先進邏輯技術進行 HBM4移轉,進而實現高效能和低功耗。其中,12奈米的基礎裸晶解決方案可讓功耗降低40%以上,現已準備就緒。3奈米基礎裸晶解決方案將於2025年底就緒。

矽光子技術可用於頻寬擴展,利用光收發器可實現高速、低能耗、可靠的數據傳輸;搭配SoIC技術,可將電子和光子裸晶堆疊在一起,實現更高的互連密度和更低的系統功耗,從電路板層到中介層的光引擎整合可提供10倍以上的功耗優勢。

台積電SoIC技術電子和光子裸晶堆疊在一起,以實現更高的互連密度和更低的功耗。取自TSMC

台積電推出車用級先進封裝解決方案,透過3D高密度金屬-絕緣體-金屬(MiM)電容,橫向溢流整合電容(LOFIC)影像感測器具備高動態範圍,可應對光線條件的突然變化。另針對車用智慧型先進駕駛輔助系統(ADAS),它在不犧牲光線性能和生成效果的情況下,提供超過100 dB的LED無閃爍動態範圍。

台積電也推出新技術支援物聯網應用,包括已開始N4e的探索性開發,旨在繼續降低Vdd (正電源電壓)。此外,超低漏電SRAM和邏輯電路進一步降低了漏電功率,從而延長電池壽命。

最新more>

熱門more>

- 51萬粉「台灣臀后」下場慘了!高雄總圖激戰片外流 檢分案調查

- 「台灣臀后」穿小白裙到案身影!身旁有個「他」 頂大學霸這原因變謎片女主

- 「拒陪睡韓男」遭暴打全身傷、手指骨折…劉力穎怒揭:搭訕男手都摸上來

- 現場照瘋傳!《三生三世十里桃花》于朦朧驚傳墜樓亡…好友悼念:笑容定格記憶中

- 公費流感疫苗10月開打!今年全面改用三價疫苗

- 「突然有念頭」大都會公園遊戲區驚見男DIY 3女蒐證怒追!噁男堅持「射出來」

- 情侶甜遊墾丁變調!36歲女陳屍海灘 男友驚嚇難承受

- 金鐘60|陳淑芳獲特別貢獻獎 「大S、瓊瑤無緣名單」評審說話了

- 高雄13歲國中女未到校 書包留房內家人急尋…只見倒臥露台冰冷身軀

- 女大生喊「對不起」仍被殺!沙鹿命案17歲少年落網 竟辯:想唱完KTV再投案